World Applied Sciences Journal 31 (10): 1837-1842, 2014

ISSN 1818-4952

© IDOSI Publications, 2014

DOI: 10.5829/idosi.wasj.2014.31.10.597

# A Novel Explicit Pulsed Dual Edge Triggered D Flip Flop

<sup>1</sup>Manan joshi, <sup>2</sup>D.S. Chauhan and <sup>3</sup>B.K. Kaushik

<sup>1</sup>DBIT Dehradun, India <sup>2</sup>UTU, Dehradun, India <sup>3</sup>IIT Roorkee, India

**Abstract:** This paper presents an efficient explicit pulsed static dual edge triggered flip flop with an improved performance. The proposed design overcomes the drawbacks of the dynamic logic family and uses explicit clock pulse generator approach to achieve dual edge triggering. The proposed flip-flop is compared with existing explicit pulsed dual edge triggered flip-flops. Based on the simulation results overall improvements of 7.45%, 13.68% and 20.03% are observed in delay, power consumption and power delay product respectively.

**Key words:** Power delay product • Flip flop • Power consumption • Propagation delay • CMOS logic • Transmission gate • Explicit pulsed.

### INTRODUCTION

Flip Flops and latches form part of clock distribution network, timing elements, memory etc in digital systems. Reducing delay and power consumption will have a deep impact on the performance of digital systems. Flip Flops affect the clock frequency, since their delay occupies a significant fraction of the clock cycle, especially in fast micro-architectures with low logic depth. Together with the circuits devoted to the clock generation and distribution, Flip Flops are part of the clock network that is responsible for 30%-50% of the whole chip energy budget [1]. Power consumption has become a significant issue in modern IC designs, especially for high-end processors and energy-aware mobile devices.

During recent past a lot of advancements have been observed in the field of Flip Flops. The earliest work on edge triggered D-Flip Flop gives the Yuan-Svensson D-Flip Flop [2] that was proposed in the year of 1996. The transistors in this flip flop have conflicting requirements and hence this circuit cannot be optimised well. The sense amplifier based flip flop [3] consisting of a sense amplifier and slave latch is very similar to a master slave flip flop. Here only one transistor is active during clock transition that increases the driving capability of the output stage and reduces power dissipation. But being a two stage, circuit it cannot reduce delay efficiently. The conditional capture flip flop [4] is an innovation where the internal

nodes switch only when the output needs to be switched. This approach can save power dissipation in a circuit. Another flip flop introduced has the advantage of being able to avoid stacking of PMOS transistors. As a consequence, low voltage and low power operation becomes feasible. The low swing clock double edge triggered flip flop[5] uses a data sampling front end and a data transferring back end and the internal nodes switch only when there is a data change. It results in reduced power consumption. Conditional discharge flip flop [6] introduced another innovation where output switches off the discharge path of first stage to prevent it from discharging and doing evaluation in succeeding clock cycles as long as the input does not change. Thus the flip flop reduces power consumption further. The conditional precharge flip flop was also introduced to save power consumption by not allowing precharging to take place as long as D and Q have similar input and output respectively. Similarly the conditional data mapping flip flop [7] reduces the dynamic power consumption by mapping the inputs to a configuration that eliminates redundant internal transitions. The data mapping is conditional i.e. when the applied input is the same as the output that results in no internal transitions. A clock branch sharing flip flop [8] reduces the number of clocked transistors and thus r educes the power consumption. In clocked Pseudo NMOS level conversion flip flop [9], Pseudo NMOS has been used for conditional discharge.

The benefits of level conversion are also used. The energy efficient dual edge triggered level converting flip flop [10] has the benefits of level conversion and data retention in sleep mode that are used to reduce switching activity and hence power consumption.

There are four main flip flop classes: master slave (MS), implicit-explicit pulsed (IP and EP), differential and dual edge triggered [11]. Recently used Transmission Gate Flip Flop is an example of Master Slave Flip Flop. Hybrid Latch Flip Flop and Transmission Gate Pulsed Latch refer to the Pulsed Flip Flop that can be used for both Implicit(IP) and Explicit(EP) operation respectively. Likewise, Conditional Capture Flip Flop is a Differential Flip Flop and Conditional Discharge Flip Flop is a Dual Edge Triggered Flip Flop. Pulse triggered flip flops have a simple structure, negative setup time and soft edge. The pulse generator of explicit pulsed flip flop is shared by neighbouring flip flops [12]. Ultra Low Voltage Logic based D Flip Flop using sub threshold voltage operated Schmitt Trigger has very low power consumption [15]. Ultra Low voltage circuits suffer from insufficient noise margin, setup timing constraints and hold time violations that require special consideration [16]. The conventional CMOS logic and pass transistor logic (PTL) styles [17] are two major architectures that are used to implement logic circuits. The PTL family [18] primarily resulted in (1) complementary PTL (CPL) (2) Transmission gate (TG) Logic. However, these pass transistor logic styles become very slow when cascaded due to the increased delay and insertion of buffers (CMOS inverters) is necessitated. This negates the advantage of low power consumption that PTL logic has. A logic style that uses a combination of PTL and CMOS will have lesser power consumption due to use of PTL and lesser delay due to drive capability of CMOS logic. The design of the proposed D Flip Flop uses both Transmission gate Logic as well as CMOS logic styles in such a way that it not only reduces the number of transistors used but also the drive capability that in turn reduces delay.

This paper introduces a new dual edge triggered Flip Flop using CMOS logic, transmission gate and pulse generator. This architecture is capable of embedding logic functions [19] and can be used for designing control units and pipelined datapath structures. It also performs charge sharing free operation more efficiently. This dual edge triggered flip flop that uses the clock pulse based approach reduces power consumption drastically in comparison to earlier reported research works [12-14]. The proposed flip flop avoids MOS transistor stacking, reduces internal node switching and as a consequence

low voltage and low power operation is possible. The two stages *i.e.* the input stage and the output stage are basically CMOS inverters that switch only when there is a data change and hence result in reduced power consumption. The pass transistors, NMOS and PMOS are used to construct the transmission gate that provides edge triggering. It results in reduction of the number of clocked transistors and power consumption.

The rest of the paper is organised as follows. Section II presents the proposed D Flip Flop with its functionality. Section III gives the Simulation Set-up used. Section IV compares the proposed D Flip Flop with architectures proposed earlier [12-14]. Finally, conclusions are drawn in section V.

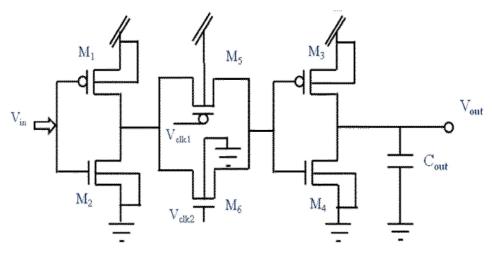

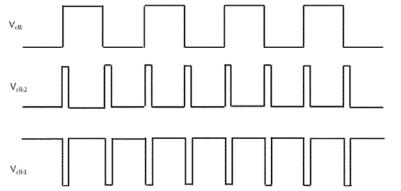

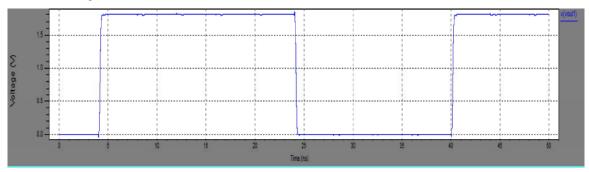

Proposed Dual Edge Triggered Flip Flop: The proposed D Flip Flop shown in Fig. 1 consists of an input and output stage that is an inverter, whereas the middle stage that allows the input to pass through only at the clock edge. The two inverters invert the signal twice and hence the output is the same as input. Two clock pulses that are generated from pulse generator are applied to the MOSFETs (M<sub>5</sub> & M<sub>6</sub>). The parasitic capacitance at the input of the output stage inverter holds the charge/signal. The NMOS (M<sub>6</sub>) serves as a good pull down device and brings the input of the output stage inverter to zero volt, whereas the PMOS (M<sub>5</sub>) serves as a good pull up device and brings the input of the output stage to  $V_{dd}$ . The Fig. 1 below shows the proposed D Flip Flop and Fig. 2 shows the clocks. In Fig. 1 clock  $V_{clk1}$  is generated from  $V_{\text{clk2}}$  by passing it through an inverter.

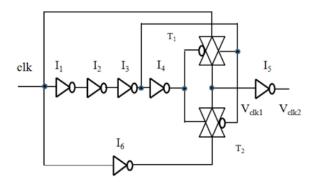

The clock  $V_{\text{clk2}}$  is generated from the clock with 50 percent duty cycle using an explicit pulse generator shown in Fig 3. The explicit pulse generator produces a pulse at every clock edge ( $V_{\text{clk2}}$ ). When  $V_{\text{clk}}$  switches from low to high, node X is pulled down by  $T_1$  and  $T_2$  pulls down node X when  $V_{\text{clk}}$  switches from high to low. This produces a pulse at every clock transition. It is essential to ensure that inverters  $I_1$  &  $I_2$  delay the effect of change in clock edge. This is achieved by increasing the length ( $I_2$ ) of the NMOS and thereby weakening it so that its turn ON is delayed. When length ( $I_2$ ) increases the resistance increases allowing NMOS to remain OFF for a longer time. The inverter also will have a longer falling edge delay.

The clock pulses shown in Fig. 2 and derived from pulse generator shown in Fig. 3 are applied to the transmission gate formed by  $M_{\scriptscriptstyle 5}$  and  $M_{\scriptscriptstyle 6}$  as shown in Fig. 1 causing edge triggering.

Power consumption of a particular clocking scheme can be represented as [5]

Fig. 1: Proposed Dual edge triggered Flip Flop

Fig. 2: Clocks applied to proposed D Flip Flop

Fig. 3: Circuit showing explicit pulse generator

$$P_{\text{clk-scheme}} = P_{\text{clk-netword}} + P_{FF} \tag{1}$$

where  $P_{\text{elk-network}}$  and  $P_{\text{FF}}$  represent power consumptions in the clock network and flip flops respectively. The total power dissipation of the clock network depends on both the clock frequency and the data rate that can be expressed as [11].

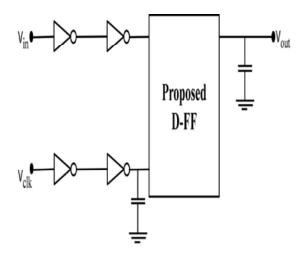

Fig. 4: Set up used for simulation

$$P_{clk-network} = V_{dd}^{2} \left[ f_{clk} \left( C_{clk} + C_{ff-clk} \right) + f_{data} \ C_{ff.data} \right]$$

(2)

A waveform of D making a  $0 \rightarrow 1$  and  $1 \rightarrow 0$  transition.

Fig. 5: Output of proposed Flip Flop  $V_{out}$

where  $f_{clk}$ ,  $f_{data}$ ,  $C_{elk}C_{ff,elk}C_{ff,data}$  are present the clock frequency, the average data rate, the total capacitance seen by clock network, the capacitance of the clock path seen by the flip flop, the Capacitance of the data path seen by the flip flop respectively. The total power dissipation in the flip flop is as follows [5].

$$PFF = \left\{ \left( \alpha_i . C_j . \gamma + \alpha_o . C_o . \gamma + C_{clk-buf} \right) V_{dd}^2 \right\}$$

(3)

where  $C_i$ ,  $C_o$ ,  $\alpha_i$ ,  $\alpha_o$ ,  $C_{clk-buf}$  is the internal node capacitance of the FF, the output node capacitance of the flip flop, the internal node transition activity ratio, the output node transition activity ratio, the capacitance of the clock buffers repectively.  $\gamma$  is 2 for double edge triggered flip flops and 1 for single edge triggered flip flops.

From the above expression (2) it is obvious that the clock power can be reduced if any of the parameters can be reduced. The reduction of  $V_{\text{dd}}$  is already the trend of contemporary design and has the strongest impact on the  $P_{\text{clk-scheme}}$  expression. By reducing the overall capacitance of the clock network, the power dissipation is reduced. Similarly, by reducing the capacitance inside a flip flop,  $C_{\text{ff,clk}}$  and  $C_{\text{ff,data}}$ , power is reduced.

From the expression (3) it is clear that power dissipation in the flip flop is reduced if any of the parameters in the expression is reduced. The internal node capacitance is reduced by keeping the number of nodes as less as possible and keeping the dimensions of the MOSFETs as small as possible. The internal node transition activity  $\alpha_i$  and output node transition activity  $\alpha_o$  is reduced by designing the circuit in such a way that the internal and external nodes switch only when the data change takes place.

The conclusions from the above three expressions are used while designing the proposed Flip Flop. Attempt is made to keep the MOSFETs  $M_1$ ,  $M_2$ ,  $M_5$  and  $M_6$  as

small as possible to reduce power consumption in the data path network.  $M_3$  and  $M_4$  are kept just large enough to provide optimum power delay product. Moreover the design of the Flip Flop is such that the internal nodes switch only when the data change takes place and hence  $\alpha_i$  and  $\alpha_o$  are reduced.

**Simulation Setup:** The set-up used in our simulations is as shown in the Fig. 5. The circuits are simulated in real environment, where the buffers (inverters) drive the flip flop inputs (data and clock) and the output drives a capacitive load of 21fF. An additional capacitance of 3fF

is placed after the clock driver. We have applied at the D input, an input data with an activity factor of 25% to reflect the average power consumption. Power consumed in the data and clock drivers is included in our measurements. Clock frequency used is 125 MHz.

#### RESULTS AND DISCUSSIONS

The simulation results are obtained using Tanner EDA in TSMC 180nm CMOS Technology. The design is simulated using the circuit at the schematic level. Table I presents the comparison between SEDNIFF Flip Flop and the proposed D Flip Flop. We analyse the two designs in view of Power Delay Product, DQ delay, CQ delay and Power Consumption.

The primary drawback of flip flop SEDNIFF is that it is composed of twenty nine transistors out of which eleven are in the latch. The pulse generator has eighteen transistors that continuously switch with clock. This results in higher average power dissipation. The pulse generator and the latch consist of stacked transistors that reduce the efficiency of the flip flop. In the proposed Flip Flop pass transistors that are used to construct the transmission gate have length (L) and width (W) that are

Table 1: Comparing the Flip Flops in Terms of Delay, Power Consumption and Power Delay Product

| Design Name | Tran count | DQ Delay (ps) | Power (µW) | PDP (fJ) | % change in PDP |

|-------------|------------|---------------|------------|----------|-----------------|

| SCDFF       | 29(17)     | 234.5         | 41.97      | 9.8      | -               |

| DEPFF       | 29(14)     | 230.2         | 37.05      | 8.53     | 12.95           |

| SEDNIFF1    | 29(11)     | 217.7         | 34.44      | 7.49     | 12.19           |

| Proposed    | $22(6)^2$  | 201.5         | 29.73      | 5.99     | 20.03           |

<sup>&</sup>lt;sup>1</sup>FlipFlop proposed in [12]

optimized to reduce power consumption and at the same time work at lower delay. Moreover the pulse generator consists of sixteen transistors and the latch consists of six transistors. This results in lower average power dissipation. Due to symmetry, scaling of the proposed flip flop is simple. Proper design of the pulse generator ensures low power consumption.

## **CONCLUSION**

This paper presented the design of a new explicit pulsed double edge triggered D Flip Flop. This flip-flop has reduced redundant switching and minimum short circuit current and hence reduced power consumption. The flip flop has least number of clocked transistors and lowest power consumption and is therefore suitable for use in high performance and low power environments. In addition to this, it is also capable of embedding logic functions and performs charge sharing free operation more efficiently.

#### REFERENCES

- Nedovic, N. and V.G. Oklobdzija, 2005. "Dual Edge Triggered Storage Elements and Clocking Strategy for Low Power Systems," IEEE Trans. VLSI Systems, 13(5): 577-590, May 2005.

- Huang, Q. and R. Rogenmoser, 1996. "Speed Optimisation of Edge-Triggered CMOS Circuits for Gigahertz Single-Phase Clocks," IEEE J. Solid-State Circuits, 31: 3, Mar. 1996.

- Nicolic, B., V.G. Oklobdzija, V. Stojanovic, W. Jia, J.K.S. Chiu and M.M.T. Leung, "Improved Sense-Amplifier-Based Flip Flop: Design and Measurements," IEEE J. Solid-State Circuits, 35: 6, June 2000.

- 4. Kong, B.S., S.S. Kim and Y.H. Jun, 2001. "Conditional-Capture Flip Flop for Statistical Power Reduction," IEEE J. Solid-State Circuits, vol. 36, no. 8, Aug. 2001.

- Kim, C. and S.M. Kang, 2002. "A Low Swing Clock Double-Edge Triggered Flip Flop", IEEE J. Solid-State Circuits, Vol. 37, No. 5, May 2002.

- Zhao, P., T.K. Darwish and M.A. Bayoumi, 2004. "High-Performance and Low-Power Conditional Discharge Flip Flop," IEEE Trans. VLSI Systems, vol. 12, no. 5, May 2004.

- 7. The, C.K., M. Hamada, T. Fujita, H. Hara, N. Ikumi and Y. Oowaki, "Conditional Data Mapping Flip Flops for Low Power and High Performance Systems," *IEEE Trans. VLSI Systems*, vol. 14, no. 12, Dec. 2006.

- 8. Zhao, P., J.M. Neely, P. Golconda, M.A. Bayoumi, R. A. Barcenas and W. Kuang, "Low Power Clock Branch Sharing Double Edge Triggered Flip Flop," *IEEE Trans. VLSI systems*, vol. 15, no. 7, July 2007.

- Zhao, P., J.B. McNealy, P.K. Golconda, S. Venigalla, M.A. Bayoumi, W. Kuang and L. Downey, 2009. "Low Power Clocked Pseudo NMOS Flip Flop for level Conversion in Dual Supply Systems," *IEEE Trans. VLSI Systems*, vol. 17, no. 9, Sept. 2009.

- Chiou, L.Y. and S.C. Luo, 2009. "Energy Efficient Dual Edge Triggered Level Converting Flip Flops with Symmetry in Setup Times and Insensitivity to Output Parasitics," IEEE Trans. VLSI Systems, vol. 17, no. 11, Nov. 2009.

- Alioto, M., E. Consoli and G. Palumbo, 2001.

"Analysis and Comparison in the Energy-Delay-Area domain of nanometer CMOS flip flops: Part II -Results and Figures of Merit," IEEE Trans. VLSI Systems, vol. 19, No. 5, May 2011.

- 12. Wu, X.X. and J.Z. Shen, "Low power explicit-pulsed triggered flip flop with robust output," *Electronic Letters*, vol. 48, no. 24, Nov. 2012.

- Phyu, M.W., W. L. Goh and K.S. Yeo, 2005. "A low-power static dual edge triggered flip-flop using an output-controlled discharge configuration," *IEEE Int. Symp. on Circuits and Systems*, Japan, May 2005, 3: 2429-2432.

- Dai Y. and J. Shen, 2010. "Structure and design method for pulse triggered flip-flops at switch level," J. Cent. South Univ. Technol., 17(6): 1279-1284.

- Lotze, N. and Y. Manoli, 2012. "A 62mV 0.13μm CMOS Standard-Cell-Based Design Technique using Schmitt Trigger Logic," IEEE J. Solid-State Circuits, vol. 47, no. 1, Jan. 2012.

<sup>&</sup>lt;sup>2</sup>In parenthesis is the transistor count of its latch

- Lutkemeir, S., T. Jungeblut, H.K.O. Burge, S. Aunet, M. Porrmann and U. Ruckert, 2013. "A 65nm 32b Subthreshold Processor with 9T multi V<sub>t</sub> SRAM and adaptive supply voltage control," IEEE J. Solid-State Circuits, vol 48, no 1, Jan 2013.

- 17. Chung, W., T. Lo and M. Sachdev, 2002. "A Comparative Analysis of Low-Power Low Voltage Dual-Edge Triggered Flip Flops," IEEE Trans. VLSI Systems, vol. 10, no. 6, Dec. 2002.

- Zimmermann, R. and W. Fichtner, 19997. "Low Power Logic Styles: CMOS versus Pass-Transistor Logic," IEEE J. Solid-State Circuits, 32(7): 1079-1090.

- Sarbishei, O. and M.M. Nejad, 2010. "A Novel Overlap based Logic Cell: An Efficient Implementation of Flip Flops with embedded Logic," IEEE Trans. VLSI Systems, vol. 18, no. 2.

- Constantino, J.B.A. and J.A.R. Madamba, 2011.

"Static dual edge flip flop implementations on the 90nm process," in Proc. IEEE 2011, 5<sup>th</sup> Asia Modelling Symp.

- 21. Phyu, M.W., W.L. Goh and K.S. Yeo, 2005. "A low-power static dual edge triggered flip-flop using an output-controlled discharge configuration," IEEE Int. Symp. on Circuits and Systems, Japan, 3: 2429-2432.

- Dai, Y. and J. Shen, 2010. "Structure and design method for pulse triggered flip-flops at switch level," J. Cent. South Univ. Technol., 17(6): 1279-1284.