World Applied Sciences Journal 29 (8): 1075-1077, 2014

ISSN 1818-4952

© IDOSI Publications, 2014

DOI: 10.5829/idosi.wasj.2014.29.08.1426

# **Recovery Boosting Technic Using Efficiency Increasing in SRAM**

### A. Geetha

Department of ECE, Bharath University, Chennai - 73, India

Abstract: High variability in nano-scaled technologies can easily disturb the stability of a carefully designed standard 6T- SRAM cell, causing access failures during a read/write operation. We propose a 7T-SRAM cell to increase the read/write stability under large variations. The proposed design uses a low overhead read/write assist circuitry to increase the noise immunity. Use of an additional transistor and a floating ground allows read disturb free operation. While the write assist circuitry provides a floating ground during a write operation that weakens cell storage by turning off the supply voltage to ground path of the cross-coupled inverter pair. This allows a high speed/low power write operation. Monte Carlo simulations indicate a 200% increase in the read stability and a boost of 124% in write stability compared to a conventional 6T-SRAM design, when subjected to random dopant fluctuations, line edge roughness and poly-granularity variations. HSPICE simulations of a 45nm 64x32 bit SRAM array designed using standard 6T and proposed 7T SRAM cells indicate a 31% improvement in write speed/write power, read power decreases by 60% and a 44% reduction in the total average power consumption is achieved with the proposed design.

Key words: Variability • SRAM • SNM • Stability • Power • Speed

### INTRODUCTION

**SRAM** is an important part of modern microprocessor design, taking a large portion of the total chip area and power. Increasing the density of SRAM caches provides an effective method to enhance system performance [1]. That has resulted in over 70% of the chip area being occupied by SRAM [1]. Scaling device size doubled the transistor count every two years according to Moore's law and hence the density of SRAM caches kept mounting every next generation [2]. However device dimensions become too small in nano-scale technologies and are more prone to variations due to manufacturing process [3]. These variations can disturb the read/write stability of a SRAM design causing reliability problems. A conventional 6T-SRAM has a poor read stability due to constraint design requirements and can suffer functional failures due to high threshold voltage variations. Statistical variability arising from the discreteness of charge and matter is a major source of threshold variation that degrades the reliability of conventional SRAM design [2]. Conventionally device sizing is used to enhance the read

stability of SRAM cell design. However conventional sizing can be ineffective in nano-scaled technologies due to large threshold variations [3, 4]. Different SRAM designs have previously been presented that use from 6 to 10 transistors to provide reliable and/or low power operation [5-9].

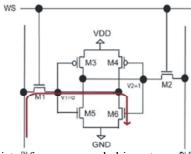

## Proposed 7T-SRAM design:

It consists of a cross-coupled inverter path (M3-M6) that does data storage and two access transistors (M1-M2) to load/retrieve data on bit lines, BL and BLB. During a write operation, the data is loaded on the bit lines and the word select signal WS is turned high. A successful write

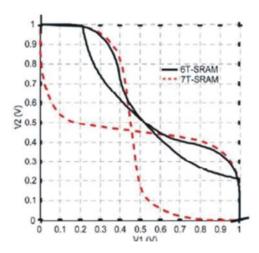

Fig. 4: Shows the read/write stability comparison using

operation occurs if the data is correctly latched in the cell [10]. The bit lines are pre-charged to the supply voltage and the word select line is turned high to retrieve data during a read operation [11]. The bit line (BL) connected to the storage node (V1) storing a '0' gets discharged. The storage node (V1) rises above '0' during a read operation due to voltage division between the access transistor (M1) and the driver transistor (M6) [12]. A read failure can occur if the voltage drop rises higher than the threshold voltage of the inverter (M3, M5).

Simulation Results and Analysis: 35nm gate-length MOS-models with no variability [10]. Conventional 6T-SRAM provides a SNM of 112 mV for a1 V supply voltage with CR=1.5 (CR = WM5/WM1 = WM6/WM2). Whereas the proposed 7T-SRAM design increases the read margin to 299 mV with CR=1, indicating a 167 % improvement as shown in Fig. 4a. This indicates a high tolerance against read failures for the proposed design because the storage nodes are not disturbed during a readoperation [13]. This enhancement in the SNM comes at the expense of an additional transistor. However, increasingdevice variability will result in further degradation of the SNM of conventional 6T-SRAM in future technologies, therefore a move to 7T or higher SRAM cell designs will benecessary to provide high stability and performance under large variations. The use of write assist transistor results in a significant increase of the WNM due to weakened cellstorage and the WNM improves by 112 % (406mV vs.861mV) at a supply voltage of 1 V.

#### CONCLUSION

Variability in nano-scaled technologies is a major challenge for reliable SRAM design. A conventional 6T-SRAM cell can't achieve high read/write stability due toconstrained design. A 7T-SRAM cell is proposed that uses separate read/write assist circuitry to provide high stability under large variations. Monte Carlo simulations indicate a 200% increase in the SNM and a 124% boost in the WNM for the proposed design [14-17]. This increase comes at the cost of anadditional transistor that has a 16% area overhead. However the use of 7T or higher SRAM designs may be necessary infuture generations due to poor stability of conventional 6T- SRAM design. A comparative analysis of a 45nm 64x32 bit SRAM array designed using conventional 6T and proposed 7T SRAM cells indicates a 31% increase in write speed and a 31% decrease in write power for the proposed design. Use of a single ended read operation results in a 60% decrease in read power, while a 44% reduction in total average power is observed for the proposed design.

### REFERENCES

- Kevin, Z., 2009. Embedded Memories for Nano-Scale VLSIs. Springer Publishing Company, Incorporated, 400.

- Brown, A.R., G. Roy and A. Asenov, 2007. Poly-Si-Gate-Related Variability in Decananometer MOSFETs With Conventional Architecture. Electron Devices, IEEETransactions on, 54(11): 3056-3063.

- Bo, Z., et al., 2007. A Sub-200mV 6T SRAM in 0.13um CMOS. In Solid-State Circuits Conference, 2007. ISSCC 2007. Digest of Technical Papers. IEEE International.

- Cheng, B., S. Roy, G. Roy, A. Brown and A. Asenov, 2006. Impact of Random Dopant Fluctuation on Bulk CMOS 6-T SRAM Scaling. in Solid-State Device Research Conference, 2006. ESSDERC 2006. Proceeding of the 36th European.

- Jawar Singh, D.K.P., Simon Hollis and Saraju P. Mohanty, 2008. A single ended 6T SRAM cell design for ultra-low-voltage applications. IEICE Electronics Express, 5(18): 750-755.

- Mizuno, H. and T. Nagano, 1996. Driving source-line cellarchitecture for sub-1-V high-speed low-power applications. Solid-State Circuits, IEEE Journal, 31(4): 552-557.

- Takeda, K., et al., 2006. A read-static-noise-marginfree SRAM cell for low-VDD and high-speed applications. Solid-State Circuits, IEEE Journal, 41(1): 113-121.

- 8. Chang, L., *et al.*, 2008. An 8T-SRAM for Variability Tolerance and Low-Voltage Operation in High-Performance Caches. Solid-State Circuits, IEEE Journal, 43(4): 956-963.

- Tae-Hyoung, K., et al., 2007. A High-Density Subthreshold SRAM with Data-Independent Bitline Leakage and Virtual Ground Replica Scheme.in Solid-State Circuits Conference, 2007. ISSCC 2007. Digest of Technical Papers.IEEE International.

- Sundarraj, M., 2013. Study Of Compact Ventilator, Middle-East Journal of Scientific Research, ISSN: 1990-9233, 16(12): 1741-1743.

- Sundar Raj, M., T. Saravanan and R. Udayakumar, 2013. Energy Conservation Protocol for Real time traffic in wireless sensor networks, Middle-East Journal of Scientific Research, ISSN:1990-9233, 15(12): 1822-1829.

- Sundar Raj, M. and T.R. Vasuki, 2013. Automated Anesthesia Controlling System, Middle-East Journal of Scientific Research, ISSN:1990-9233, 15(12): 1719-1723.

- Sundar Raj, M., T. Saravanan and R. Udayakumar, 2013. Data Acquisition System based on CAN bus and ARM, Middle-East Journal of Scientific Research, ISSN: 1990-9233, 15(12): 1857-1860.

- 14. Kabiru Jinjiri Ringim, 2013. Understanding of Account Holder in Conventional Bank Toward Islamic Banking Products, Middle-East Journal of Scientific Research, 15(2): 176-183.

- 15. Muhammad Azam, Sallahuddin Hassan and Khairuzzaman, 2013. Corruption, Workers Remittances, Fdi and Economic Growth in Five South and South East Asian Countries. A Panel Data Approach Middle-East Journal of Scientific Research, 15(2): 184-190.

- Sibghatullah Nasir, 2013. Microfinance in India Contemporary Issues and Challenges. Middle-East Journal of Scientific Research, 15(2): 191-199.

- 17. Mueen Uddin, Asadullah Shah, Raed Alsaqour and Jamshed Memon, 2013. Measuring Efficiency of Tier Level Data Centers to Implement Green Energy Efficient Data Centers, Middle-East Journal of Scientific Research, 15(2): 200-207.