Middle-East Journal of Scientific Research 23 (3): 442-445, 2015 ISSN 1990-9233 © IDOSI Publications, 2015 DOI: 10.5829/idosi.mejsr.2015.23.03.22089

# A Survey on Map Design of Low-Complexity Turbo Decoder Architecture

Venkatesh. N. and Benister Joseph Pravin

Department of ECE Sathyabama University, Chennai, India

**Abstract:** In engineering constrained wireless communication applications, turbo codes were considered since they promote low transmission energy disbursement. Turbo decoders with low complexity for low processing energy expenditure are to be used that result in minimization of overall energy consumption. This paper aims at atomization of low complexity turbo decoders into its basic ACS activities and observe them using ACS unit using MAP algorithm. Unlike other turbo codes MAP focuses on optimal error correction. Xilinx is the tool used to establish that our architecture employs a better energy consumption reduction than LUT-Log-BCJR architectures.

Key words: Energy-Efficient • Error-Correcting Code (ECC) • MAP • Log-BCJR algorithm • Turbocode

# **INDROUCTION**

Turbocodes are the classes of forward error correction codes that are well adoptable of making error free communication in Digital processing. Initially these turbo codes are generated in IEEE conference of conversation in Geneva, 1993. Experts call these codes as the Error Correcting Codes or Turbocodes [1]. The main article in turbocodes is to deliver double data throughput at a given power or delivers single data throughput with half the power. It also provide virtually error free communications at data per power effeciencies. There are several codes that yields the performance close to the shannon limits predicted by shanon [2]. They are Block codes, Reed-soloman codes, convolutional codes and concatenation codes. For the best case, those codes can have the SNR ratio greater by 2.5dBs within Shannon limits. The breakthrough appeared in 1983 where parallel concatenated codes were invented which was later called by Turbo codes [3]. Parallel concatenation codes uses interleavers in between the successive encoders in order to scramble the codes. Since the interleaver length is too big in PCC, Maximum likelihood decoding would be very complex. So the alternate approach for PCC is MAP (Maximum a posterior) decoder. This algorithm increases number of iterations thus the bit error rate reduces up to 0.0004 by simulation and SNR ratio would be-0.15dB [4]. In addition to this, Turbocodes are used to reduce the energy consumption. In order to reduce the

comprehensive energy consumption LUT-log-BCJR algorithm is used. This facilitates the energy reduction up to 10%. But the main problem previling in this algorithm is less suite for high throughput and high energy scenearios also it uses complex windowing techniques in order to detect and correct errors [5]. A suitable replacement of this algorithm is MAP algorithm which is more stochastic than BCJR algorithm.

System Description: In communication systems individually, wireless sensor networks in order to achieve the performance condition\ size and speed are the effective factors. Turbo codes are very much useful in such pratical applications with their error correcting capabilities. Many algorithms are useful for turbo codes for error correcting technique. But the optimal error correction is done by using MAP (Maximum A Posterior) technique. Due to its recursive computation, it is difficult to construct high speed MAP Decoder [6]. This problem is overcome by constructing MAP decoder using SB/DB decoding technique. The real MAP decoder algorithm are not really the pratical algorithm for implementation in real systems. The MAP algorithm is calculating complex and sensitive to SNR mismatch and inaccurate about noise levels. This algorithm also requires non-linear functions for computations. Fixed point representation for the MAP decoding variables usually requires bits between 16 to 24 for QPSK applications. Based on the above requirements, MAP algorithm is not

implemented in the chip. So, logarithmic version of MAP and soft output viterbi algorithm (SOVA) is used. This algorithm are less sensitive to SNR mismatch and the fixed point representation of variables are approximated to 8 bits. But SOVA have low BER performance but logarithmic MAP decoder can have good BER performance and it has highest computational complexity [7]. The basis of turbo coding is to introduce the parity bits in the data to be transmitted through the channel. This parity bits are used to obtain the original bits from the received data. In data transmission, Turbo codes help to achieve the near Shannon limit performance. Turbo codes show their outstanding performance in terms of bit rate and SNR. BER (Bit Error Rate) can be calculated in terms of ratio of bits wrongly received to the total number of bits. Turbo encoder transmits the encoded bits forms the input for turbo decoder turbo decoder decodes information iteratively. MAP algorithm is used in turbo decoding technique. It is based on the principle of receiving the soft input data being "1? or "0?. MAP algorithm intention, whether the accepted data are either "0? or "1?. This is probable by means of trellis. Trellis is the State Transition Table consisting of encoder input/output. Based on this information[8], MAP decoder computes the probability of the encoder being in a particular state. Based on the soft data, parity value and the weighted data from previous state, the probability of data entered either "1? or "0?. MAP decoder computes the weight of each data for both forward and reverse directions. This results in computation of both forward and reverse metrices. The computation of the probabilities is done iteratively to obtain a dependable result. Once the result is considered dependable, one can make the final decision as to whether the data entered is 0 or 1. Turbo decoder can be implemented both in Log MAP and MAX MAP algorithm and log MAP algorithm shows better performance but utilises more resources and run at very lower frequencies. Turbo decoder requires soft input and soft output decoding algorithm. It consists of components which exchange the information iteratively. Between iterations this information is recorded. MAP decoders are superior to its communication performance. MAP decoders throughput is 20 times than the normal decoder i.e turbo decoder. The log likelihood ratio is the probability that the received data bit is 0 divided by the probability of received data bit is 1. By taking the logarithm it have the positive value then the received bit is "1 otherwise it is .,0

### **Proposed Method**

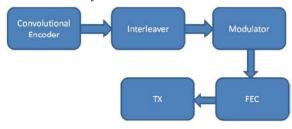

Turbo-Encoder System

**Channel Encoder Structure**

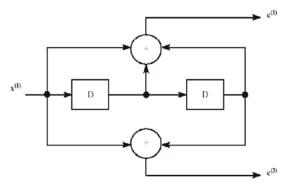

In turbo encoder generator representation shown the shift register hardware connection are tapping to the modulo-2. A turbo decoder generator vector represents the tapping position for an output A"0"prerepresent no connection and a "1" prerepresent a connection.. for instance, the two generator vector binary value for both g1 and g2.then the output terminals denotes as 1 and 2.

The code rate r=k/n for a convolutional code.

### r=k/n

### where,

k is the number of parallel input information bits and n is the number of parallel output encoded bits at one time interval. The restraint length K for a convolutional code is defined as

# K=m+1

#### where,

m is the maximum number of stages (memory size) in shift register.x= $\{1011\}$  produces the output encoded sequence c= $\{11, 10, 00, 01\}$ . "Mode" is used to con?gure the dual-mode LLR calculator. When "Mode" is active low, the dual-mode LLR calculator is in SB mode.

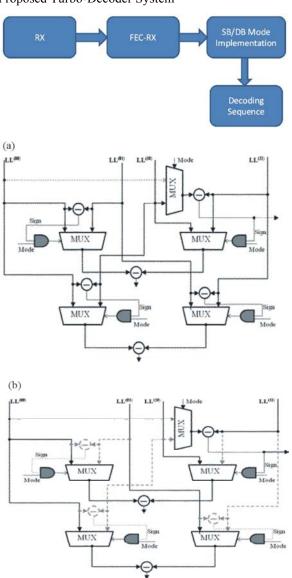

Proposed Turbo-Decoder System

Fig. 6: Logic blocks of dual mode LAPO in (a) SB mode, (b) DB mode.

## Literature Survey:

A Low-Complexity Turbo Decoder Architecture for Energy-Efficient Wireless Sensor Networks.

Liang Li, Robert G. Maunder and Bashir M. Al-Hashimi

The main objective of this paper is to facilitate low transmission energy consumption and also to reduce the overall energy consumption in WSN using turbo codes(Turbo decoder and encoder). The Methodology used in this paper are Decompose LUT-Log-BCJR architectures into its most fundamental add compare select action and behave them using a novel low-complexity ACS unit. The main Drawbacks in this paper is Latency is high.

- Area-Efficient and High Speed ML MAP Processor Design Using DB/SB Decoding Technique

- P. Maniraj kumar and Dr. Sutha

The main equitable of this paper is to enhance the speed and reduce the size in order to meet the performance requirements in networks.

The Methodology used in this paper proposes a ML-MAP algorithm with dual mode SB/DB decoding in order to avoid recursive computations in MAP decoder.

The main drawback in this paper is it Occupies a moderate area and high latency.

• Design and Implementation of a Parallel Turbo-Decoder ASIC for 3GPP-LTE

Christoph Studer and Christian Benkeser

A White paper on 3GPP-LTE discuss concepts and architectures which allow for the power.

Efficient implementation of high-throughput parallel turbo-decoding. The Methodology used in this paper address to implement the parallel turbo decoder that reaches the 326.4Mb/s LTE peak data rate using soft input and soft output decoders that operate in parallel.

The main Drawbacks in this paper is Utilization of more hardware components.

An Efficient 4-D 8PSK TCM Decoder Architecture

Jinjin He, Zhongfeng Wang and Huping Liu

This paper presents an efficient architecture for a 4-D eight-phase-shift-keying trellis coded modulation (TCM) decoder. This scheme significantly reduces the required computations without degrading the performance. The Methodology used in this paper combines the algorithm on BMs(Branch Metrices) and the algorithm on PMs(path Metrices), the hybrid algorithm can reduce the calculation required by the conventional algorithm on PMs by 50%. The Drawbacks in this paper are Low packet delivery ratio.

#### CONCLUSION

An extensive survey of the various existing turbo decoders, BCJR architecture consumes high latency and hardware complexity Also, it detects and corrects random errors..Burst errors cannot be tolerated in communication channels. The proposed Turbo decoder based on SB/DB (Single binary/double binary)mode to reduce the hardware utilization and also reduce the power consumption Up to 74%. Adapting DB and SB mode dynamically depends upon the channel conditions in various environments.

### REFERENCES

- Corke, P., T. Wark, R. Jurdak, H. Wen, P. Valencia and D. Moore, 2010. Environmental wireless sensor networks, Proc. IEEE, 98(11): 1903-1917.

- Li, L., R.G. Maunder, B.M. Al-Hashimi and L. Hanzo, 2010. An energy-efficient error correction scheme for IEEE 802.15.4 wireless sensor networks, Trans. Circuits Syst. II, 57(3): 233-237.

- Studer, C., C. Benkeser, S. Belfanti and Q. Huang, 2011. Design and implementation of a parallel turbo-decoder ASIC for 3GPP-LTE, IEEE J. Solid-State Circuits, 46: 8-17.

- May, M., T. Ilnseher, N. Wehn and W. Raab, 2010. A 150 Mbit/s 3GPP LTE turbo code decoder, in Proc. Design, Autom. Test in Euro. Conf. Exhib. (DATE), pp: 1420-1425.

- Wong, C., Y. Lee and H. Chang, 2009. A 188-size

2.1 mm reconfigurable turbo decoder chip with parallel architecture for 3GPP LTE system, in Proc. Symp. VLSI Circuits, pp: 288-289.

- Akyildiz, I.F., W. Su, Y. Sankarasubramaniam and E. Cayirci, 2008. Wireless sensor networks: A survey, Comput. Netw.: Int. J. Comput. Telecommun. Netw., 52: 292-422.

- Howard, S.L., C. Schlegel and K. Iniewski, 2006. Error control coding in low-power wireless sensor networks: When is ECC energy-efficient? EURASIP J. Wirel. Commun. Netw., pp: 1-14.

- Robertson, P., P. Hoeher and E. Villebrun, 1997. Optimal and sub-optimal maximum a posteriori algorithms suitable for turbo decoding, Euro. Trans. Telecommun., 8(2): 119-125.